Yepyeni üretim teknolojileri için yol bulma, araştırma ve geliştirme döngüsü uzadıkça, dökümhanelerin müşteri gereksinimlerini karşılamak için düğümlerinin yenilenmiş sürümlerini tanıtması gerekiyor. TSMC Perşembe günü N3’ünü resmen açıkladı Önümüzdeki üç yıl içinde öncü çipler oluşturmak için kullanılacak (3nm sınıfı) üretim süreçleri ailesi. N3’ün temel özelliklerinden biri, çip tasarımcılarına performans, güç ve kalıp boyutunu optimize etmek için ek yollar sağlayan FinFlex teknolojisidir.

TSMC’nin N3 süreç teknolojileri ailesi, tamamı FinFlex’i destekleyecek toplam beş düğümden oluşacaktır. Ürün grubu, bu yılın sonlarında yüksek hacimli üretime (HVM) girecek olan orijinal N3’ü içeriyor ve ilk çipler 2023’te teslim edilecek; Watt başına performans ve süreç penceresi iyileştirmeleri ile N3E; Ek performans geliştirmeleri ile N3P; Artırılmış transistör yoğunluğuna sahip N3S ve artırılmış voltaj, gelişmiş güç dağıtımı desteğine sahip N3X; ve ultra yüksek performanslı uygulamalar için artırılmış saat hızı potansiyeli.

TSMC’nin duyurduğu gibi, bu yıl içinde orijinal N3 düğümünde çip yapmaya başlayacak. Bu süreç teknolojisi, büyük ölçüde, pahalı yongalar (veya pahalı cihazlar için yongalar) geliştiren, her türlü performans, güç ve donanımdan yararlanan mobil ve yüksek performanslı bilgi işlem (ASIC’leri, CPU’ları, GPU’ları vb. okuyun) endüstrilerinden erken benimseyenler için tasarlanmıştır. alan (PPA) iyileştirmeleri ve bunlar için ödeme yapmaya hazırlar.

Orijinal N3 düğümü, belirli uygulamalar için beklenenden daha düşük verim anlamına gelebilecek nispeten dar bir işlem penceresine sahip görünüyor. Sonuç olarak, TSMC, süreç penceresini iyileştiren (ve dolayısıyla verimi artıran) ve aynı zamanda (aynı güç ve karmaşıklıkta) performansı %18 artıran ve aynı zamanda gücü %34 azaltan (aynı hızda ve transistörde) N3E düğümünü hazırlıyor. sayım) N5 ile karşılaştırıldığında. Esasen, N3E daha hızlı ve daha enerji verimli çipler sağlar, ancak bunun maliyeti biraz daha düşük transistör yoğunluğudur. N3E önümüzdeki haftalarda risk üretimine girecek, bu nedenle 2023’ün ortalarında HVM için hazır olacak.

İleriye dönük olarak, TSMC, daha yüksek saatlere (örneğin CPU’lar) ihtiyaç duyan uygulamalar için performansı artırılmış N3P’yi ve daha fazla transistörden (örneğin, AI hızlandırıcıları, GPU’lar, ASIC’ler, vb.) yararlanan çipler için transistör yoğunluğu optimize edilmiş N3S işlem teknolojilerini sunacaktır. Bu düğümlerin 2024’te kullanıma sunulması bekleniyor. Bu arada, 2025 yılına kadar TSMC, aşırı voltajları, yüksek sürücü akımlarını destekleyecek ve işlemciler gibi ultra yüksek performanslı yongaları etkinleştirecek çok özel bir düğüm olan N3X’e sahip olacak. Görünüşe göre N3X, güç dağıtımını iyileştirmek için gelişmiş bir arka uç (BEOL) sunacak gibi görünüyor, ancak spekülasyon yapıyoruz.

TSMC’nin N3’ünü diğer dökümhane düğümlerinden ayıracak şeylerden biri de şirketin FinFlex teknolojisidir. FinFlex, çip geliştiricilerin performansı, güç tüketimini ve alanı olağanüstü ayrıntı düzeyiyle dengelemesini sağlamalıdır.

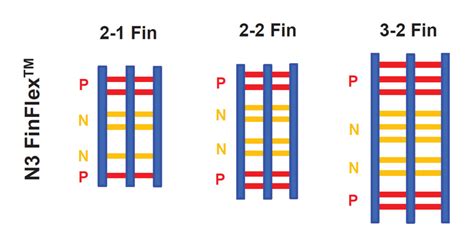

Çip üzerinde bir sistem tasarlarken, günümüzde geliştiriciler bir SoC içindeki her blok için bir kitaplık/transistör türü seçmek zorundadır. Örneğin, kalıp boyutunu ve güç tüketimini azaltmak için çift kapılı tek kanatlı (2-1) FinFET’leri kullanabilirler; performans, alan ve gücü dengelemek istiyorlarsa çift kapılı çift kanatlı (2-2) transistörleri seçebilirler; veya maksimum performans için üç kapılı çift kanatlı (3-2) FinFET’leri seçebilirler, ancak bu ek güç tüketimi ve kalıp boyutu anlamına gelir. Bu, tüm durumlar için uygun değildir, bu nedenle N3 ve FinFlex ile SoC tasarımcıları her SoC bloğunda farklı FinFET türlerini karıştırıp eşleştirebileceklerdir. Bu, deneyimli geliştirme ekiplerinin hedeflerine ulaşmak için benzersiz bir PPA dengesi sunacak özel yapılandırmalar oluşturmasını sağlayacaktır.

FinFlex, özelleştirilmiş / optimize edilmiş düğümlerin veya hatta özelleştirilmiş kitaplıkların yerini almaz çünkü düğümler ve kitaplıklar çok daha fazla sadece farklı FinFET yapılandırmaları içerir. Ancak FinFlex, ileriye dönük güç, performans ve maliyet optimizasyonları için özellikle faydalı olacaktır. TSMC, FinFlex’in elektronik tasarım otomasyonu (EDA) ortakları tarafından desteklendiğini, bu nedenle bu yetenekten yararlanmanın nispeten kolay olması gerektiğini söylüyor. Bu arada, AI özellikli EDA araçları FinFlex için destek kazandığında, ikincisi daha da kullanışlı hale gelecektir.

Gerçeği söylemek gerekirse, eski tarz CPU yaratıcıları performanslarını en üst düzeye çıkarmak için tasarımlarını transistör seviyelerinde ayarladılar, ancak bu tür metodoloji yıllar önce mikroişlemciler aşırı derecede karmaşık hale geldiğinde terk edildi. FinFlex’in önde gelen EDA programları tarafından desteklenmesiyle, çip geliştiricilerin benzersiz optimizasyonları tanıtmak ve tasarım hedeflerini tutturmak için benzersiz FinFET yapılandırmalarını kullanmaları daha kolay olmalıdır.

Daha yüksek performans, daha düşük güç ve alanı optimize etmek için transistör konfigürasyonlarını ayarlamak, çok yönlü kapı (GAA) transistörlerinin tasarım gereği desteklediği bir özelliktir. Bir blok içinde farklı FinFET’lerin karıştırılmasını ve eşleştirilmesini sağlamak, TSMC’nin N3’ünün rekabet gücünü artırabilir.