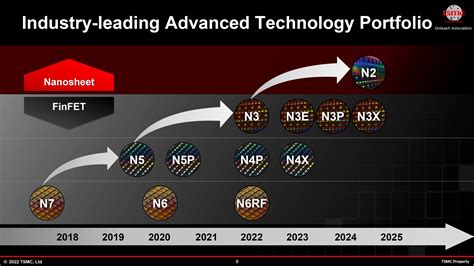

TSMC’nin N3 (3nm sınıfı) fabrikasyon süreçleri ailesi, performans ve güç açısından bir dizi fayda sağlasa da, dökümhanenin ilk N3 düğümünün çok yüksek maliyetleri yaygın kabulü engellemektedir. Şaşırtıcı olmayan bir şekilde, şirketin bir rapora göre çip tasarımcılarının ilgisini çekmek için 3nm üretim fiyatlarını düşürmeye hazırlandığı söyleniyor. Sürücülerim.

Bu noktada yayınlanan herhangi bir TSMC’nin N3 teklifleri ve fiyatları söylenti olarak kabul edilmelidir, ancak TSMC’nin N3E sürecindeki üretim maliyetlerinin ilk N3’tekinden daha düşük olması muhtemeldir. Şirketin N3P, N3S ve N3X gibi diğer N3 sınıfı düğümlerde üretim için ne kadar ücret talep edeceği henüz belli değil. 3nm üretim fiyatlarının düşürülmesi bu düğümlere daha fazla müşteri çekecek, ancak bu bir gecede olacak bir şey değil.

TSMC’nin ilk N3 üretim teknolojisinin (N3B olarak da bilinir) yalnızca Apple tarafından kullanılacağı söyleniyor çünkü şirket, dökümhanenin en gelişmiş düğümleri diğerlerinden önde benimsemeye istekli en büyük müşterisi. Ancak N3, kullanımı pahalı bir teknolojidir. N3, 25 katmana kadar yoğun bir şekilde aşırı ultraviyole (EUV) litografi kullanıyor. Çin Rönesansıve her bir EUV tarayıcının maliyeti, konfigürasyona bağlı olarak artık 150 milyon – 200 milyon dolar arasındadır. Bu tür üretim araçlarıyla donatılmış fabrikaların değerini düşürmek için TSMC, N3 süreci ve haleflerinde üretim için daha fazla ücret almak zorundadır.

Bazıları, TSMC’nin N3 yonga levhası başına 20.000 ABD Doları’na kadar – N5 yonga levhası başına 16.000 ABD Doları’na kadar – ücret alabileceğini söylüyor. Artan maliyetler, AMD, Broadcom, MediaTek, Nvidia ve Qualcomm gibi şirketler için daha düşük kar anlamına geliyor; bu nedenle çip geliştiricileri, gelişmiş tasarımları nasıl oluşturduklarını ve en son düğümleri nasıl kullandıklarını yeniden değerlendiriyor.

“Anlamlı olduğuna inanıyoruz [N3] China Renaissance analisti Szeho Ng, optimize edilmiş sürüm N3E’nin hazır olacağı 2H 2023’te olacak” diye yazdı. MTK) ve ASIC (yani, MRVL, AVGO, GUC) muhtemelen N4/5’te kalacak ve bize göre ilk N3 sınıfı baskınları olarak N3E’yi seçecekler. Bu arada, temel N3’ün (N3B olarak da bilinir) benimsenmesinin büyük ölçüde Apple ürünleriyle sınırlı olacağına inanıyoruz.”

Ortaklarını N3 sınıfı süreç teknolojilerini kullanmaya teşvik etmek için TSMC’nin bu düğümler için fiyat tekliflerini düşürmeyi düşündüğü bildiriliyor. Özellikle, TSMC’nin N3E işlemi EUV’yi yalnızca 19 katmana kadar kullanır ve üretim açısından biraz daha düşük karmaşıklığa sahiptir ve bu nedenle kullanımı daha ucuzdur. TSMC, karlılığa zarar vermeden N3E üretim fiyatlarını düşürebilir. SRAM hücre ölçeklendirme söz konusu olduğunda N3E, N5’e göre sıfır avantaj sağlar; bu, N3/N3B’de yapılanlarla karşılaştırıldığında daha büyük kalıp boyutları anlamına gelir.

AMD, 2024’te çıkacak Zen 5 tabanlı tasarımlarından bazıları için bir N3 düğümü kullanmayı planladığını kamuoyuna duyurdu ve Nvidia’nın, aynı zaman diliminde piyasaya çıkacak olan yeni nesil Blackwell mimarisi tabanlı GPU’ları için N3’ü benimsemesi bekleniyor. Yüksek maliyetler nedeniyle, N3 sınıfı düğümlerin benimsenmesinin belirli ürünlerle sınırlı olması bekleniyor – bu nedenle fiyatları düşürmek muhtemelen çip tasarımcılarının benimseme stratejilerini yeniden gözden geçirmelerine neden olacaktır.

TSMC’nin N3’ünde başka bir sorun daha var: düşük verim. Bazı tahminlere göre verimler %60 ile %80 arasındadır ve kaynaklar DigiTimes (üzerinden Dan Nystedt) %50’nin altında olduklarını gösterir. Bununla birlikte, yalnızca Apple’ın bu üretim teknolojisini kullandığı ve şirketin çok gizli olduğu bilindiğinden, ilk N3 yongalarının verimleriyle ilgili herhangi bir ayrıntı büyük bir tuz tanesi ile alınmalıdır.